# Comp 790-184: Hardware Security and Side-Channels

Lecture 4: Side-Channel Defenses

February 18, 2025 Andrew Kwong

#### **Outline**

- How to mitigate side-channel attacks

- Non-interference property

- Constant-time programming

- Constant-time under speculation

#### **Attack Examples**

#### Example #2: RSA cache vulnerability

Example #1: termination time vulnerability

```

def check_password(input):

size = len(password);

for i in range(0,size):

if (input [i] == password[i]):

return ("error");

return ("success");

```

```

for i = n-1 to 0 do

r = sqr(r)

r = r mod n

if e<sub>i</sub> == 1 then

r = mul(r, b)

r = r mod n

end

end

```

Example #3: Meltdown

```

Ld1: uint8_t secret = *kernel_address;

Ld2: unit8_t dummy = probe_array[secret*64];

```

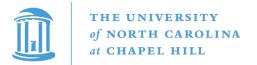

# Who to blame? Who should fix the problem?

#### **Break SW and HW Contract**

# **Software Developer's Problem**

#### Software developers:

- Need to write software for devices with unknown design details.

- How can I know whether the program is secure running on different devices?

# **Hardware Designer's Problem**

#### Hardware designer:

- Need to design processors for arbitrary programs.

- How to describe what kind of programs can run securely on my device?

# **Example: Termination Time Vulnerability**

How can we fix this?

```

def check_password(input):

size = len(password);

for i in range(0,size):

if (input [i] != password[i]):

return ("error");

return ("success");

```

Make the computation time **independent** from the secret (password)

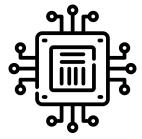

## **Non-Interference Example**

- Intuitively: not affecting

- Any sequence of low inputs will produce the same low outputs, regardless of what the high level inputs are.

#### **Non-Interference: A Formal Definition**

ullet The definition of noninterference for a deterministic program P

#### Non-Interference for Side Channels

ullet The definition of noninterference for a deterministic program P

What should be included in the observation trace?

# **Understanding the Property**

```

\forall M1, M2, P

M1_{L} = M2_{L} \land (M1, P) \xrightarrow{\mathbf{01}_{*}} M1' \land (M2, P) \xrightarrow{\mathbf{02}_{*}} M2'

\Rightarrow 01=02

```

## Consider input as part of M

- What is M<sub>L</sub>?

- What is M<sub>H</sub>?

- What is 0 ?

```

def check_password(input):

size = len(password);

for i in range(0, size):

if (input [i] == password[i]):

return ("error");

return ("success");

```

# **Constant-Time Programming**

• For any secret values, a program always takes the same amount of time for the same input when executing on the same machine, and this holds for arbitrary inputs.

# **Data-oblivious/Constant-time programming**

How do we deal with conditional branches/jumps?

How do we deal with memory accesses?

• How do we deal with arithmetic operations: division, shift/rotation, multiplication?

Your Code

Compiler

Hardware

For details on real-world constant-time crypto, check this out: https://www.bearssl.org/constanttime.html

```

def check_password(input):

size = len(password);

for i in range(0,size):

if (input [i] != password[i]):

return ("error");

return ("success");

```

```

def check_password(input):

size = len(password);

dontmatch = false;

for i in range(0, size):

dontmatch |= (input [i] != password[i])

return dontmatch;

```

## **Real-world Crypto Code**

from libsodium cryptographic library:

```

for (i = 0; i < n; i++)

d |= x[i] ^ y[i];

return (1 & ((d - 1) >> 8)) - 1;

```

Compare two buffers x and y, if match, return 0, otherwise, return -1.

## **Eliminate Secret-dependent Branches**

- An instruction: cmov\_

- Check the state of one or more of the status flags in the EFLAGS register (cmovz: moves when ZF=1)

- Perform a move operation if the flags are in a specified state

- Otherwise, a move is not performed and execution continues with the instruction following the cmov instruction

#### **Conditional Branches**

```

if (secret) x = e

x = (-secret & e) | (secret - 1) & x

test secret, secret // set ZF=1 if zero

cmovz r2, r1 // r2 for x, r1 for e

```

#### **More Conditional Branches**

```

if (secret)

res = f1();

else

res = f2();

```

```

r1 ← f1();

r2 ← f2();

mov r3, r1

test secret, secret

cmovz r3, r2

// res in r3

```

#### Potential problems:

- What if we have nested branches?

- What if when secret==0, f1 is not executable, e.g., causing page fault or divide by zero?

- What if f1 or f2 needs to write to memory, perform IO, make system calls?

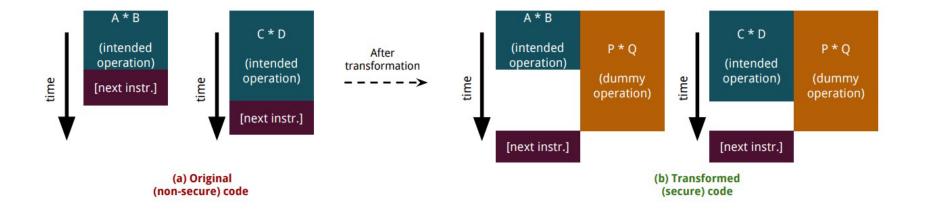

- Hardware assumption: what if cmovz will be executed as soon as the flag is known (e.g., speculative execution)?

# **Memory Accesses**

```

a = buffer[secret]

```

```

for (i=0; i<size; i++)

{

tmp = buffer[i];

xor secret, i

cmovz a, tmp

}</pre>

```

- Performance overhead.

- Techniques such as ORAM can reduce the overhead when the buffer is large

23

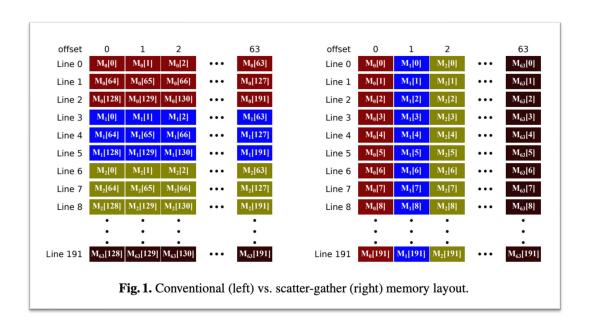

# **An Optimization**

We can reduce the redundant accesses by only accessing one byte in each cache line.

```

for (i=0; i<size; i++)

{

tmp = buffer[i];

xor secret, i

cmovz a, tmp

}</pre>

```

```

offset = secret % 64;

for (i=0; i<size; i+=64)

{

index = i+offset;

tmp = buffer[index];

xor secret, index

cmovz a, tmp

}</pre>

```

# **OpenSSL Patches Against Timing Channel**

CacheBleed, an attack leaks SSL keys via **L1 cache bank conflict**.

25

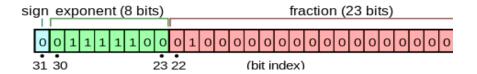

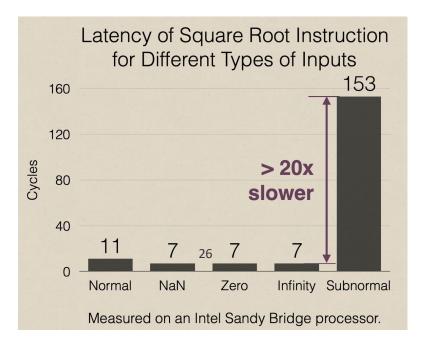

# **Arithmetic Operations**

#### Subnormal floating point numbers

#### The Problem and A Solution

Rane et al. Secure, Precise, and Fast Floating-Point Operations on x86 Processors. USENIX'16

#### **Constant-time ISA**

- Some efforts:

- ARM Data Independent Timing (DIT)

- Intel Data Operand Independent Timing (DOIT)

ARM DIT: https://developer.arm.com/documentation/ddi0601/2020-12/AArch64-Registers/DIT--Data-Independent-Timing Intel DOIT: https://www.intel.com/content/www/us/en/developer/articles/technical/software-security-guidance/best-practices/data-operand-independent-timing-isa-guidance.html

# **Constant-time under Speculation**

• What problems arise?

THE UNIVERSITY

of NORTH CAROLINA

at CHAPEL HILL